MAR DO

Voices: eSilicon's Jack Harding Pg 22

Understanding FFT plots Pg 24

Prying Eyes: One sensor does the work of many Pg 26

Design Ideas Pg 51

Tales from the Cube: Conspiracy theory Pg 66

# FPGAS RESHAPE EMBEDDED DESIGN

Page 38

TAMPER-RESISTANT SMART POWER METERS RELY ON ISOLATED SENSORS

Page 29

#### WHATEVER HAPPENED TO MY DYNAMIC RANGE?

Page 47

CLICK HERE TO **START** a FREE <u>e-newsletter</u> subscription

## "I need to see the most signal detail."

#### **Look no further.** InfiniiVision scopes are engineered for the best signal visibility.

#### It's a bold claim — let us prove it to you.

Agilent engineered the custom MegaZoom III technology in our Agilent InfiniiVision scopes so you get the best possible signal visibility on every measurement you make.

- 1. **Fastest uncompromised update rate** shows you critical signal detail and gives you statistically valid measurement results in seconds.

- Industry's only hardware accelerated mixed signal oscilloscope gives you analog, logic, and protocol views.

- Customize your scope with software applications including mask testing, RS-232/UART, CAN/LIN and more.

100 MHz to 1 GHz MSO and DSO models

Take the 5-minute Scope Challenge online and register to win a free Agilent MS07104 Scope. www.agilent.com/find/bestscopes

# OVER 400,000 PRODUCTS IN STOCK FROM MORE THAN 400 SUPPLIER PARTNERS\*

Constant of the second

ARABARAR

An additional 1,000,000+ components can be sourced at www.digikey.com

The industry's broadest product selection available for immediate delivery

ORPORATION

I-KEY

\*Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2009 Digi-Key Corporation

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

# **NI LabVIEW.** Limited Only by Your Imagination.

#### Real-Time and Embedded

Signal Processing

sing High-Performance Test

Industrial Control

PRODUCT PLATFORM

NI Advanced Signal Processing Toolkit

NI Motion and Vision Modules

NI LabVIEW MathScript

NI CompactRIO Embedded Hardware Platform Ambient cofounders and research students from the University of Illinois chose NI LabVIEW software to create the first thoughtcontrolled wheelchair. Using LabVIEW – a graphical system design environment ideal for signal synthesis, frequency analysis, and digital signal processing – they developed sophisticated algorithms that translate neurological signals into commands, empowering people with disabilities.

#### >> Explore the thought-controlled interface at ni.com/imagine/sp

#### 866 337 5041

# Whatever happened to my dynamic range?

477 If your testing results don't closely approximate the silicon vendor's specification claims, question your assumptions before concluding that your supplier is inflating the numbers.

by Steve Green, Cirrus Logic

#### FPGAs reshape embedded design

38 Although its use requires a significant change in design methodology, FPGA technology has become a valuable weapon in the embedded-system developer's arsenal.

by Warren Webb, Technical Editor

#### Tamper-resistant smart power meters rely on isolated sensors

29 Utilities are pushing to replace old electromechanical meters with microcontroller-based smart meters that, in addition to their intelligence and communication ability, are also tamper-proof. There is also a growing market for individual small power meters and an emerging market for metering at the server, or individual-appliance-network, level. *by Margery Conner, Technical Editor*

# DESIGNIDEAS

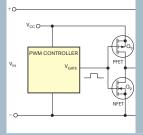

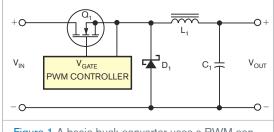

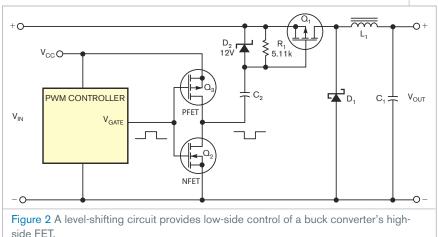

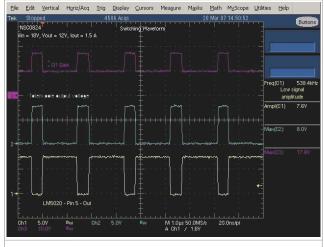

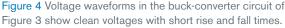

- 51 Buck converter uses low-side PWM IC

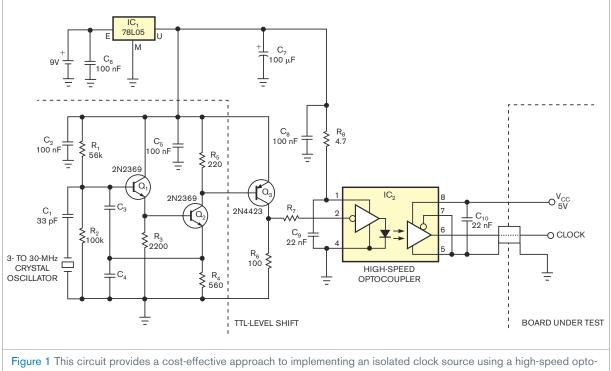

- 53 Isolated clock source acts as test generator

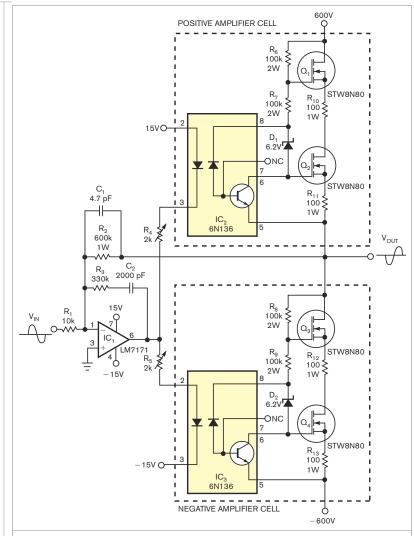

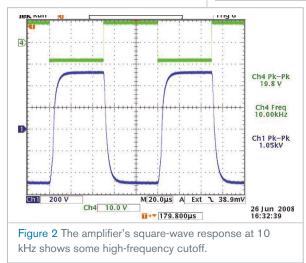

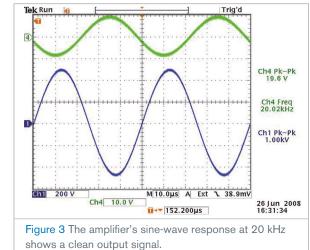

- 54 Class AB inverting amp uses two floating-amplifier cells

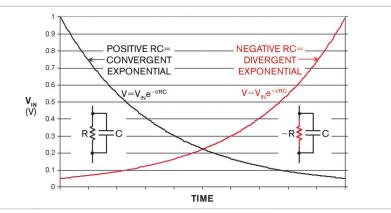

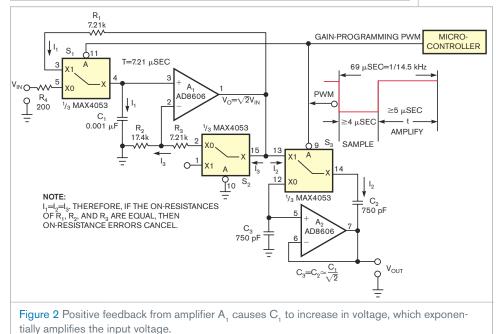

- 56 DPGA conditions signals with negative time constant

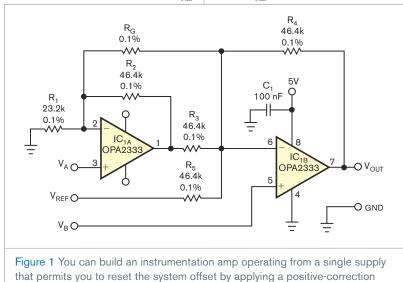

- 58 Instrumentation amplifier compensates system offset from single supply

# it's everybody's <u>business</u> to get answers as <u>fast</u> as yesterday.

Does your enterprise software help give you the insight to keep up with the pace of demand?

ask for people\_ready enterprise high tech solutions

microsoft.com/hightech

# **contents** 3,19,09

- 13 AFS Nano speeds 5000-element design simulations

- 14 DDR3 test suite features 2G transfer/sec logic-state analysis

- 16 Lithium-ion cell-measurement instruments offer48 24-bit-resolution inputs

- 16 DSP core supports 4G wireless infrastructure

- 20 One radio-test platform addresses development, production environments

- 20 Mezzanine module uses FPGA technology

- 22 Voices: Chip design in recession: a view from an ASIC consolidator

# DEPARTMENTS & COLUMNS

- 8 **EDN.comment:** Museum contends with multimedia rights

- 24 Baker's Best: Understanding FFT plots

- 26 Prying Eyes: One sensor does the work of many

- 66 Tales from the Cube: Conspiracy theory

# PRODUCT ROUNDUP

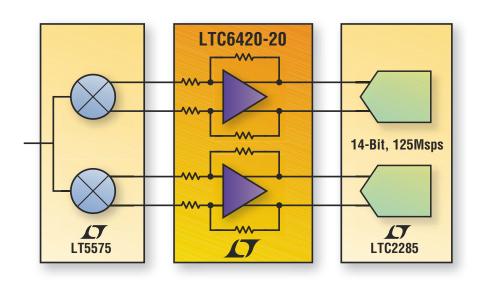

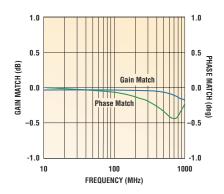

- 62 Amplifiers, Oscillators, and Mixers: Programmable oscillators, current-sense amplifiers, amplifier front ends, and more

- 63 **Embedded Systems:** Fanless computers, Wi-Fi development kits, analog inputs, and more

- 64 Integrated Circuits: 8-bit ADCs and 16-bit DACs

- 65 **Test and Measurement:** Universal counters and 16-channel test modules

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80129-2945. Barch, CO 80163-7500. EDN® copyright 2009 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year, Canada, \$229.99 one year, (includes 7% GST, GST#123397457); Mexico, \$229.99 one year, air expedited, \$339.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 604. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication?/volume 54, Number 6 (Pinted in USA).

# The Newest Optoelectronics

#### Kingbright

High Brightness LEDs www.mouser.com/ kingbright/a

PACIFIC SILICON SENSORS SEOUL SEMICONDUCTOR 3M TOUCH SYSTEMS

## New Products from:

PCB PolyLEDs www.mouser.com/ avagotechnologies/a

#### LedEngin, Inc.

LZ4-4xxx10 Serially Connected MCPCB www.mouser.com/ ledengin/a

SHARP, MICROELECTRONICS OF THE AMERICAS GM5BW High Power White LEDs www.mouser.com/ Sharpsma/a

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 390 leading suppliers.

a tti company The Newest Products For Your Newest Designs

www.mouser.com

Over A Million Products Online

# EDN at edn.com

EXPANDED ENGINEERING COVERAGE PLUS DAILY NEWS, BLOGS, VIDEO, AND MORE.

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### TGSM/GPRS power amplifiers use CMOS technology

This latest reverse-engineering effort involves the Axiom AX502 CMOS power amplifier.

→www.edn.com/article/CA6639868

#### **MEMS-based inertial sensor** is not your grandfather's gyroscope

The IC Insider looks at a MEMS-based gyroscope in microscopic detail, and finds that the ingenuity in this sophisticated sensor goes far beyond the process technology used to sculpt its mechanical features. →www.edn.com/article/CA6614434

#### Tips for designing ultralowpower systems

Follow these tips to save power in batterypowered, microprocessor-based systems. →www.edn.com/article/CA6617214

#### The online version of EDN's 2009 DSP Directory-a drastically expanded version of what appeared in these pages last issue-is available. The directory allows you to guickly home in on DSP devices and cores that meet your application needs.

www.edn.com/dspdirectory

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### Verifying FPGA designs: simulate, emulate, or hope for the best?

Simulation is a fact of life for many FPGA users today. But when is it time to stop simulating and just drop the design into the chip?

→www.edn.com/article/CA6636508

#### Lattice launches midrange FPGAs at cellular and access networks →www.edn.com/article/CA6638968

LEDs for lighting: Efficiency is not enouah

→www.edn.com/090319toca

#### First Solar breaks solar energy's \$1-per-watt barrier

→www.edn.com/article/CA6640264

A tale of two digital-video converters →www.edn.com/article/CA6636515

# EDN INNOVATION AWARDS

EDN will announce the Innovator of the Year and the Innovations of the Year at an awards ceremony in San Jose, CA, on March 30. If you can't join us there, check edn.com to find out who took home top honors. Read more about the winners in our April 23 issue. →www.edn.com/innovation

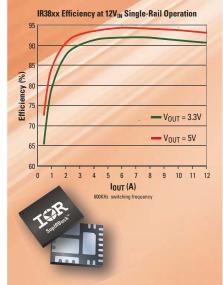

# **High Density** and High Performance

IR's SupIRBuck™ **Integrated Regulators deliver** benchmark efficiency for data center and consumer applications

#### Sup/RBuck Advantages:

- Integrates IR's high performance synchronous buck control ICs and benchmark HEXFET® trench technology MOSFETs

- 8-10% higher efficiency compared to monolithic Power IC two-stage solution

- High density compared to equivalent discrete solution

For more information call 1 800 981 8699 or visit us at www.irf.com/dcdc

## International **ICR** Rectifier THE POWER MANAGEMENT LEADER

EDN.COMMENT 2

#### BY RICK NELSON, EDITOR-IN-CHIEF

# Museum contends with multimedia rights

herever technology goes, legal issues regarding copyright ownership seem to follow. When law and technology collide, it's often over piracy and DRM (digital-rights management). But it turns out that technology can raise rights issues even when no technological DRM schemes or deliberate at-

tempts at piracy are involved.

One such instance came to my attention on a recent visit to LACMA (Los Angeles County Museum of Art, www.lacma.org). I was there to learn about the prequalification testing the museum and its consultants performed before installing a campuswide WLAN (wireless local-area network). You can read the details in a related article (**Reference 1**).

One feature of LACMA's WLAN is that it delivers multimedia content to visitors equipped with museum-issued PDAs (personal digital assistants). "Traditionally, museums have audio tours and paper-based content," says Peter Bodell, LACMA's chief information officer. "So, we stepped up and said, 'All right, we need to go to the next level; we need to get it to multimedia.""

From a visitor's perspective, the

implementation is impressive. On arriving at the museum, you can check out a tablet PC. As you stroll about the museum, you can key in three-digit codes near each object that give you access to associated multimedia content. You can listen to audio content while examining similar works on the tablet's screen. As you tour the museum, you can select "favorites." When you get home, you'll have received an e-mailed link to your own virtual gallery, in which you can review your favorites and do more research.

The museum has asked an independent organization to conduct a study of visitor acceptance of the multimedia system, but Jane Burrell, vice president for education and public programs, says that initial indications are favorable. "People love the content," she says. "They've really been excited."

Museum personnel are as pleased with the system as visitors seem to be. "It's a great opportunity for us," says Burrell. "One of the things we hear from our curators all the time is, 'We want to write more. There is so much more we want to say about our objects.' But there is only so much that

people can read in the galleries. We have strict guidelines for how much written text we can have in the galleries, and visitors can absorb only so much. But, with the ability to show images, we can tell a different kind of story—one that we couldn't tell with a label."

But telling that differ-

ent kind of story presents its own challenges, which can be as significant as the technical ones Bodell faced when trying to implement a WLAN that could handle the mix of traffic that PDAs, staff and visitor laptops, and VOIP (voice-over-Internet Protocol) handsets generate.

Content creation is itself a challenge, as Burrell and her staff work to produce multimedia programming for the museum's vast collection. But DRM issues are proving to be particularly challenging. Clearing the rights to use videos has been particularly difficult. "We've had so many people turn us down for video—just small documentary filmmakers who thought, 'OK, this is my chance to get rich," she says. "We have only limited funding for the rights, so we've had to say, 'We just can't afford it.""

Another problem is that many museums that might be willing to share content simply aren't set up to address the rights issues that arise. LACMA staffers calling to request rights, Burrell says, get bounced from department to department, or their calls don't get returned.

And that's too bad. There's no technical solution to the problem. The problem may solve itself as multimedia capabilities expand to many other museums. And that expansion seems inevitable. "A lot of modern artists are starting to work with technology as a medium," Bodell notes. As museums adopt technology to support those artists, it would be the ideal time to provide multimedia content to visitors and to establish procedures for obtaining rights from and granting them to other institutions. Museums and their visitors will be much the richer.EDN

#### REFERENCE

Nelson, Rick, "The art of wireless," *Test & Measurement World*, March 2009, pg 20, www.tmworld.com/ article/CA6639355.

Contact me at melson@reedbusiness.com.

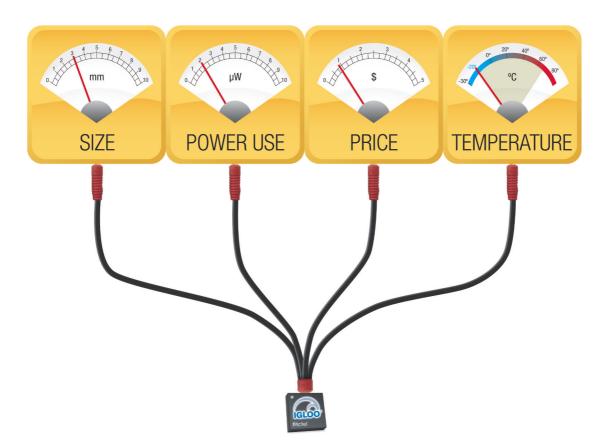

# How to pick the perfect inductor for your LED driver application

IC reference designs are a good start. But what if you want to optimize the driver inductor for size, efficiency or price?

Or evaluate newer, high performance parts that weren't available

when the reference design was created? Then you'll want to check out the new

#### Our new LED Design Center lets you:

- Search by IC to find all matching inductors

- Compare DCR, current rating, size and price

Analyze all core and winding losses

- Request free evaluation samples

#### www.coilcraft.com/LED

fect LED driver inductor, mouse over to www.coilcraft.com/LED

LED Design Center on the Coilcraft web site. It's filled with interactive tools that let you compare hundreds of inductors for all LED driver topologies, including SEPIC.

To start your search for the perinductor, mouse lcraft.com/LED

Coilcraft

# The path of least resistance

# for Transmission. Line Solutions

Connectors. Cables. Final Inch<sup>®</sup> Sudden Service<sup>®</sup> Samtec transmission line solutions provide the path of least resistance for routing signals from one location to another, when signal integrity, electromagnetic interference, pin mapping and/or power requirements present design challenges.

TRANSMISSION LINE SOLUTIONS

#### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark.finkelstein@reedbusiness.com 1-781-734-8431

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-408-421-3799; judy.hayes@reedbusiness.com

VICE PRESIDENT, EDITORIAL DIRECTOR Karen Field, 1-781-734-8188; kfield@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

EXECUTIVE EDITOR Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

> SENIOR ART DIRECTOR Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

> > ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

> EMBEDDED SYSTEMS Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187;

bdipert@edn.com MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116:

rcravotta@edn.com

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test and Measurement World edndesianideas@reedbusiness.com SENIOR ASSOCIATE EDITOR Frances T Granville 1-781-734-8439; fax: 1-303-265-3131;

f.granville@reedbusiness.com

ASSOCIATE EDITOR

Maura Hadro Butler 1-617-276-6523; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198

Melissa Annand, Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

> CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net Nicholas Cravotta.

editor@nicholascravotta.com

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

**PRODUCTION** Dorothy Buchholz,

Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

#### EDN EUROPE Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650;

fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA

Susie Newham, Managing Director susie.newham@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@rbichina.com.cn

EDN JAPAN Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.geffreemag. com/edn. Reed Business Information, 8878 S Barrons Bivd, Highlands Ranch, C0 80129-2345. Include your mailing label.

# PERFORMANCE

## From the machined interconnect component leader

From automotive systems to telecommunications, superior performance demands connections that are precise, consistent and reliable. Mill-Max Mfg. Corp. components offer:

- Secure, low-noise connections.

- .008" to .102" (0,20 2,59 mm) pin acceptance.

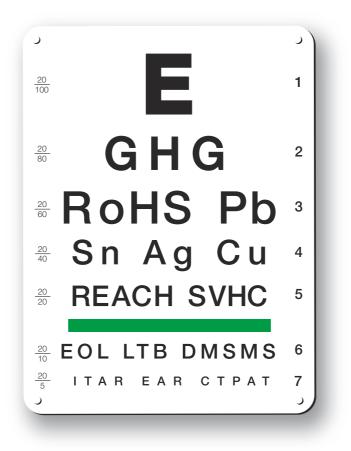

- 35 high-reliability, multi-finger contact clip designs.

- High-grade materials and quality control standards.

- RoHS and non-RoHS plating options.

Press-Fit Interconnects

Spring-Loaded Contacts

.050" (1,27 mm) Grid SMT Board-to-Board Interconnects

Mill-Max Mfg. Corp. Connect with the best.

To view our Design Guide, new product offerings and order free samples, visit

www.mill-max.com/EDN582

# PROVEN Critical Component Integrity DC-DC CONVerters DC-DC Converters 20 to 10,000 vbc output

Military Components -55° to +85°C Operating Temp Military Environmental Screening Available 3.3 to 500 VDC Outputs M/MV Series Isolated - Regulated

#### Wide Input Range

8 to 60 VDC Input 2 to 100 VDC Output Isolated-Regulated OR/IR/JR/KR Series 2-20 Watts

36 to 170 VDC Inputs Terminal Strips - Thru Hole 3.3 to 48 VDC Outputs Single and Dual Output LV/HV Series

Also Ac-DC single and 3 Phase. Power Factor Corrected. 3 Watts to 2000 Watts Models.

Call Toll Free: 800-431-1064

Fax: 914-738-8225

#### 2 to 5000 VDC Outputs Ultra Miniature

Surface Mount and Thru Hole Single and Dual Isolated Outputs Military Upgrades Available AV/AV/SM/AVR Series

100 to 10,000 VDC Output Proportional Control Up to 10 Watts VV Series

Programmable to 6000 VDC Output **HVP Series**

Military Applications -40° and -55° to +85°C **Operating Temperatures** Wide Input Range 3.3 to 350 VDC outputs in 1/2 Brick and Ful Brick Military Upgrades Available LF/LM/FM Series

HIGH POWER-Wide Input Range 2 to 350 VDC Output Isolated to 300 Watts in 1/2 and Full Brick LP/HP/XP Series

5 to 500 VDC Output to 50 Watts Wide Input Range Isolated Regulated QP Series

Electronics. Inc. 143 Sparks Ave., Pelham, NY 10803

#### www.picoelectronics.com

Complete Listing of Entire Product Line DC-DC Converters • AC-DC Inductors • Transformers and Inductors. E Mail: info@picoelectronics.com

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

# PFC controller achieves 96% efficiency

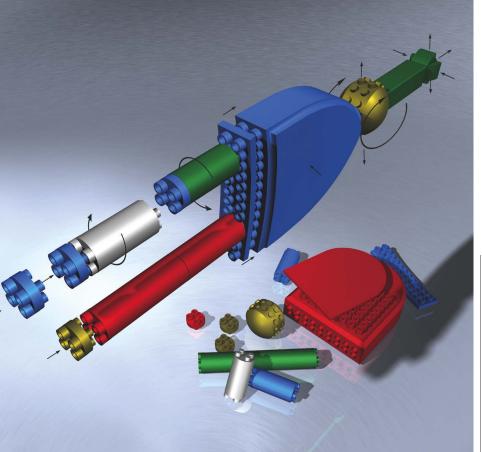

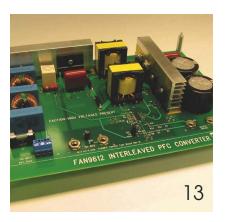

airchild Semiconductor has introduced the FAN9612 two-phase BCM (boundary-conduction-mode) PFC (power-factor-correction) controller for 100 to 1000W power systems. Driving external, high-voltage FETs, the device can realize efficiencies of 96% and targets use in two-phase, interleaved PFC control. Dual-phase operation improves efficiency and allows you to reduce the input filter size by 10%.

BCM represents the precise transition point between CCM (continuous-conduction mode)

The FAN9612 evaluation board gives you a quick start in the design of a dual-phase boundary-conduction-mode PFC power supply.

and DCM (discontinuous-conduction mode). In CCM, the PFC inductors continuously carry current; in DCM, the inductors "run dry"-that is, go to zero current-for part of the switching cycle. With BCM, each inductor goes to zero current, and the device then switches back on. The controller can automatically disable one of the two phases when driving light loads to improve efficiency.

The device features overcurrent protection and power-limit sensing for each channel, input brownout detection, and input overvoltage protection. You can design in soft start, and the restart operating frequency is above the audio range. The inductor size you select and the input voltage determine a switching speed of 18 to 600 kHz. The device also provides for input voltage feedforward to improve line regulation.

The FAN9612 provides PFC for digital TVs, desktop and entry-level server computers, frontend-telecom systems, and industrial-power systems. It comes in a 16-pin SOIC package, operates in the −40 to +125°C temperature range, and sells for \$1.30 (1000).–by Paul Rako ▷ Fairchild Semiconductor, www.fairchild semi.com. FEEDBACK LOOP "It's time the FPGA vendors paid attention to the hardware engineers that carry the water in this industry before we replace FPGAs with multicore SOCs."

-Reader and self-described "hardware guy" Mike Vis, in EDN's Feedback Loop, at www. edn.com/article/CA6633947.

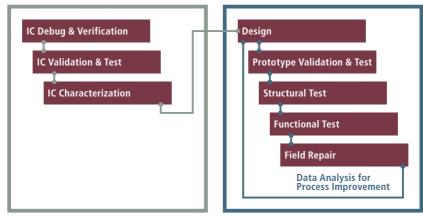

#### AFS Nano speeds 5000-element design simulations

Berkeley Design Automation has announced its AFS Nano, a version of the company's AFS (Analog FastSpice) with a 5000-element capacity limit that costs only \$1900 for a one-year license. Targeting IC-block-level designers using Linux or Solaris platforms, AFS Nano includes Synopsys (www.synopsys.com) HSpice and Cadence Design Systems (www.cadence.com) Spectre netlist support. It also features Cadence Virtuoso ADE (Analog Design Environment) integration. AFS Nano performs ac, dc, noise, transient, sweep, and Monte Carlo analyses.

AFS Nano enables IC designers to design and characterize their blocks at least two times faster than and for a fraction of the

cost of other Spice simulators, the company reports, adding that it can deliver foundry-certified true-Spice-accurate waveforms five to 10 times faster than competing simulators for even moderately sized blocks—for instance, those having 1000 elements. The company estimates that engineers use 50% of Spice simulators for block-level runs that would comfortably fit within AFS Nano's capacity limit. (For more on AFS, which supports 1 million-element analog, mixed-signal, and RF designs, see "Simulation gets speed, capacity boost," *EDN*, Jan 22, 2009, pg 26, www.edn.com/article/ CA6629472.)—**by Rick Nelson**

**Berkeley Design Automation**, www.berkeley-da.com.

# pulse

### DDR3 test suite features 2G transfer/sec logic-state analysis

gilent Technologies has introduced a comprehensive DDR (doubledata-rate) 3 protocol-debugging and validation-test suite for digital-system designers who develop computer and embedded-memory applications. The test platform includes the 2-GT/sec (gigatransfer/ sec) 16962A plug-in logicanalysis module for the company's 16901A and 16902A logic-analyzer mainframes. The test suite also includes a probing portfolio for DDR3 BGAs (ball-grid arrays) and DIMMs (dual-in-line memory modules)

and a DDR3-compliance and -performance-measurement environment.

The test suite enables research and development engineers who integrate memory controllers with the DDRmemory devices in the memory subsystem to perform interoperability testing. This testing is a major challenge for many designers because manufacturers often develop the memory-controller design in-house and integrate it with IP (intellectual property) they acquire from third parties.

Within the past year, the

The 68-channel 16962A module, which plugs into the manufacturer's logic-analyzer mainframes, triggers on and captures DDR3 bus transactions at 2G transfers/sec in the state-analysis mode.

The probes work with oscilloscopes and logic analyzers to perform physical-layer and functional tests.

use of DDR3 has significantly increased in both computers and embedded-memory designs because DDR3 devices provide higher performance and consume less power than do previous-generation DDR2 devices. To ensure that the technology is testable, engineers must take into account test-and-measurement requirements when they write specifications for complex, high-speed computer systems. Measurements are central to diagnosing problems and proving that the corrections to those problems work correctly. By contributing to standards groups, such as JEDEC (Joint Electronic Device Engineering Consortium), Agilent ensures that new designs are testable and guarantees that the company's products ensure specification compliance.

The DDR test suite, which includes the \$38,135 16962A

module with 4 million-pattern memory, 2-GT/sec state speed, and 2-GHz triggersequence speed, reliably triggers on and captures 1.6-GT/ sec DDR3 1600 signals. When designers use this module with the new DDR3 probing system and analysis software, it provides full test capability for system integration in the memory industry. On embedded-system designs, the W3630A-series DDR3 BGA probes, with prices starting at \$400, provide direct access to the DRAM contacts with low capacitive loading and minimal impact on signal integrity. The probes work with oscilloscopes and logic analyzers to perform physical-layer and functional tests. In server and desktop applications, the \$40,800 N4835A DDR3slot interposer enables nonintrusive memory-bus access through a slot connector at speeds to 1.6 GT/sec. The slot interposer provides quick and easy access to industry-standard DDR3 DIMMs, including 240-pin packages.

In addition to announcing an ensemble of DDR-testing hardware tools, Agilent introduced what it calls the industry's first DDR2 and 3 protocolcompliance and analysis software tool, the \$5500 B4622A, which will help to reduce memory designers' troubleshooting time and increase productivity and efficiency in DDR-design validation. This tool, which works with all of the manufacturer's current DDR2 and 3 test equipment, provides timing and protocol-violation checks, automated physical-address-trigger setup, and an overview of system performance through bus-statistic information and a histogram view of address access.-by Dan Strassberg Agilent Technologies,

www.agilent.com/find/ddr.

#### **DILBERT By Scott Adams**

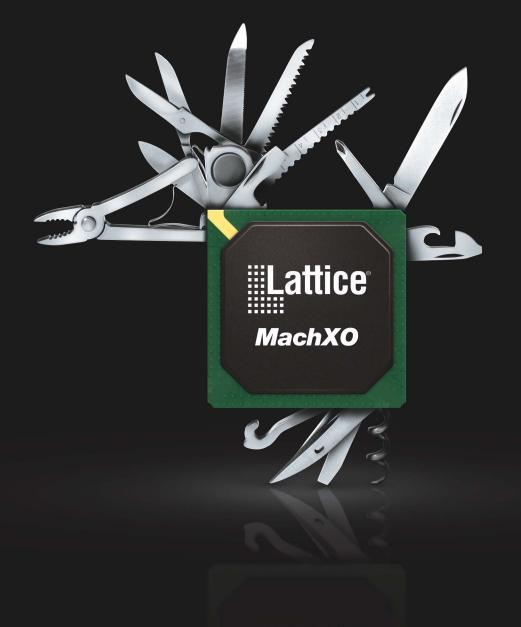

## MachXO. THE ALL-IN-ONE PLD.

**Do more with the most versatile, non-volatile PLD for low-density applications.** Loaded with flexible user I/Os, embedded memory, PLLs, and more—now you have the freedom to create and design with a single, easy-to-use, instant-on, and secure PLD.

Discover all you can do with the MachXO PLD family at: latticesemi.com/machxo

# pulse

### Lithium-ion cell-measurement instruments offer 48 24-bit-resolution inputs

$D_{ata}^{ata} Translation has announced its Voltpoint series of voltage-measurement instruments for lithium-ion cell-by-cell determination. Each Voltpoint is a stand-alone box offering 48 24-bit-resolution inputs over a sampling range of <math display="inline">\pm\,100V$ ,

each with its own sigma-delta ADC for direct connection to a PC through USB or Ethernet. The LXI (LAN-extensions-forinstrumentation)-compatible instruments can make highvoltage, high-precision batterystack and cell-balance measurements in commercial and

The Voltpoint series of voltage-measurement instruments for lithium-ion cell-by-cell determination offers 48 24-bit-resolution inputs over a sampling range of  $\pm$ 100V, each with its own sigma-delta ADC for direct connection to a PC through USB or Ethernet.

military hybrid-vehicle applications. They accept direct voltage inputs of any value in the range of  $\pm 100V$  from a single cell or from a series of stacked cells. In addition, the instruments can make motor-shunt measurements. Each of the 48 input channels offers 1000V channel-to-channel galvanic isolation. Maximum error is 3 mV for any input range.

Channels operate simultaneously at throughput rates as high as 10 Hz per channel. The instruments feature 16 optoisolated digital-I/O lineseight input lines and eight output lines-for monitoring and driving relays. Voltpoint instruments feature eight isolated digital-input lines that operate from 3 to 28V dc, with a maximum switching time of 2 msec. The instruments can directly drive relays using eight isolated digital-output lines. The outputs incorporate solidstate relays that operate at  $\pm$ 30V and 400 mA peak ac or dc with a maximum switching time of 2 msec. The digital-I/O lines feature channel-to-channel isolation as great as 250V between digital-I/O lines. Using every other line doubles the isolation but halves the number of usable I/O lines. The instruments support software triggering to initiate measurements.

The instrument comes with the software necessary to enable measurements as soon as you take it out of the box. The vendor offers software supporting the Voltpoint, including IVI-COM (interchangeablevirtual-instrument-communication) drivers, .NET class libraries, and software-development kits. Voltpoint is available in the DT9873 version for USB, which costs \$7995, and the DT8873 version for Ethernet LXI, which costs \$8495. Data Translation has begun shipping both versions.-by Rick Nelson Data Translation, www.

datatranslation.com.

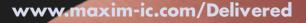

#### DSP CORE SUPPORTS 4G WIRELESS INFRASTRUCTURE

Ceva's Ceva-XC DSP core employs the company's Ceva-X architecture to support 3.5 and 4G wireless designs. The new architecture accommodates one, two, or four vector-communication units alongside a single general computational unit to provide hardware support for as many as 64 simultaneous 16×16bit MAC (multiply/accumulate) operations or 128 16×8-bit MAC operations when using all four vector units. Each vector unit is a 256-bit SIMD (single-instruction/multipledata) engine using a three-way VLIW (very-long-instruction-word) architecture that supports as many as three parallel instructions, with each instruction operating on 256bit registers.

Each engine can incorporate op-

tional instruction sets to better balance between performance and cost to support transmitter functions, floating-point operations, and the CORDIC (coordinate-rotation-digital-computer) algorithm. Additional advanced hardware includes support for MIMO (multiple-input/multipleoutput) detectors; channel estimation; and bit-chain processing for interleavers, scramblers, and FEC (forward-error-correction) encoders.

The execution units combine with the memory subsystem to enable a software implementation for LTE (long-term-evolution) Class 5 or WiMax (worldwide-interoperabilityfor-microwave-access) II designs that must support a downlink data rate of 300 Mbps with  $4 \times 4$  MIMO. The memory subsystem employs AXI (advanced-extensible-interface) master and slave system buses that are configurable between 64- and 128-bit widths, and it includes an APB (advanced-peripheral-bus) 3 interface to support slow devices.

The memory subsystem supports caches; tightly coupled memories; and interfaces for emulation, profiling, and real-time trace modules. It supports optional EEC (extended error correction) for memory error detection and correction. The DMA (direct-memory-access) engine supports 2-D transfers that can operate in background data transfers and data-rate-matching modes.

For an expanded description of this product, go to www.edn.com/ 090319pa.-by Robert Cravotta Ceva, www.ceva-dsp.com.

# 03.19.09

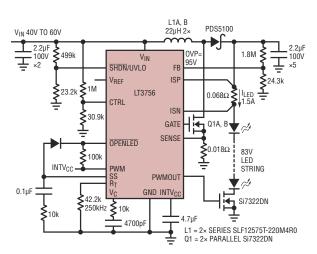

### 100V Controller Drives High Power LED Strings from Just about Any Input – Design Note 461

by Keith Szolusha

#### Introduction

Strings of high power solid-state LEDs are replacing traditional lighting technologies in large area and high lumens light sources because of their high quality light output, unmatched durability, relatively low lifetime cost, constant-color dimming and energy efficiency. The list of applications grows daily, including LCD backlights and projection, industrial and architectural lighting, automotive lights, streetlights, billboards and stadium lights.

As the list expands, so does the range of  $V_{\rm IN}$  for the LED drivers. LED drivers must be able to handle wide ranging inputs, including transient voltages of automotive batteries, a wide range of other batteries and wall wart voltages. For LED lighting manufacturers, applying a different LED driver for each application means stocking, testing and designing with a number of controllers. It would be better to use just one that can be applied to many solutions.

The LT3756 high voltage LED driver features a unique topological versatility that allows it to be used in boost, buck-boost mode, buck mode, SEPIC, flyback and other topologies. Its high power capability provides potentially hundreds of watts of LED power over a wide input voltage

range. Its 100V floating LED current sense inputs provide accurate LED current sensing. Excellent PWM dimming architecture produces high dimming ratios.

A number of features protect the LEDs and surrounding components. Shutdown and undervoltage lockout, when combined with analog dimming derived from the input, provide the standard ON/OFF feature as well as a reduced LED current should the battery voltage drop to unacceptably low levels. Analog dimming is accurate and can be combined with PWM dimming for a wide range of brightness control. Soft-start prevents spiking inrush currents. The <u>OPENLED</u> pin informs of open or missing LEDs and the SYNC (LT3756-1) pin can be used to sync switching to an external clock. The FB voltage loop limits the max V<sub>OUT</sub> to protect the converter in the case of open LEDs.

The 16-pin IC is available in a tiny QFN (3mm  $\times$  3mm) and an MSE package, both thermally enhanced. For lower input voltage requirements, the 40V<sub>IN</sub>, 75V<sub>OUT</sub> LT3755 LED controller is a similar option.

$\sigma$ , LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Figure 1. A 125W, 83V at 1.5A, 97% Efficient Boost LED Driver for Stadium Lighting

#### Boost

Lighting systems for stadiums, spotlights and billboards require huge strings of LEDs running at high power. The LT3756 controller drives up to 100V LED strings. The 125W LED driver in Figure 1 has a 40V–60V input.

The high power gate driver switches two 100V MOSFETs at 250kHz. This switching frequency minimizes the size of the discrete components while maintaining high 97% efficiency, producing a less-than-50°C discrete component temperature rise—more manageable than the heat produced by the 125W LEDs.

Even if PWM dimming is not required, the PWMOUT MOSFET is useful for LED disconnect during shutdown. It prevents current from running through the string of LEDs.

If the LED string is removed, the FB constant-voltage loop takes over and regulates the output at 95V. Without overvoltage protection, the LED sense resistor would see zero current and the output cap voltage would go over 100V, exceeding several max ratings. While in OVP OPENLED goes low.

#### **Buck Mode**

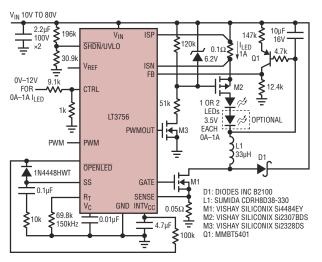

When  $V_{IN}$  is higher than  $V_{LED}$ , the LT3756 can serve equally well as a buck mode LED driver. The buck mode LED driver in Figure 2 operates with a wide 10V-to-80V input range to drive one or two LEDs at 1A.

PWM dimming requires a level-shift from the PWMOUT pin to the high-side LED string. The max PWM dimming ratio increases with higher switching frequency, lower PWM dimming frequency, higher  $V_{IN}$  and lower LED power. In this case, a 100:1 dimming ratio is possible with a 100Hz dimming frequency and a 48V input. Although higher switching frequency is possible, the duty cycle has its limits. Generous minimum on-time and minimum off-time restrictions require a frequency on the lower end of its range (150kHz) to meet both the harsh high-V<sub>IN</sub>-to-low-V<sub>LED</sub> (80V<sub>IN</sub> to one 3.5V LED) and low-V<sub>IN</sub>-dropout requirements (10V<sub>IN</sub> to 7V<sub>LED</sub>).

OVP of the buck mode LED driver has a level shift as well. Without the level-shifted OVP network tied to FB, an open LED string would result in the output capacitor charging up to  $V_{IN}$ . Although the buck mode components will survive this scenario, the LEDs may not survive being plugged into a potential equal to  $V_{IN}$ .

| Data Sheet Download |  |

|---------------------|--|

| www.linear.com      |  |

#### Buck-Boost Mode

A common LED driver requirement is that the ranges of both the LED string voltage and the input voltage are wide and overlapping. In fact, some designers prefer to use the same LED driver circuit for several different battery sources and several different LED strings. Such a versatile configuration trades some efficiency, component cost, and board space for design simplicity, and time-to-market.

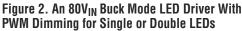

The buck-boost mode driver in Figure 3 uses a single inductor. It accepts inputs from 9V to 36V to drive 10V–50V LED strings at 400mA.

The inductor current is the sum of the input current and the LED string current; the peak inductor current is equal to the peak switching current. Below 9V input, CTRL analog dimming scales back the LED current to keep the inductor current under control. UVLO turns off the LEDs below  $6V_{IN}$ .  $C_{OUT}$ , DI and MI can see voltages as high as 95V here.

#### Conclusion

The LT3756 controller is a versatile high power LED driver. It has all the features required for large (and small) strings of high power LEDs. Its high voltage rating, optimized LED driver architecture, high performance PWM dimming, host of protection features and accurate high side current sensing make the LT3756 a single-IC choice for a variety of lighting systems.

For applications help, call (408) 432-1900, Ext. 3801

# No need to duplicate yourself

## BuyerZone saves you time and money on COPIERS AND MORE.

Get free advice, pricing articles, ratings and quotes on Business Purchases from digital copiers, to phone systems, to payroll services and more. Visit BuyerZoneBusiness.com today to make fast and efficient business purchase decisions. At BuyerZone, you're in control. We're just here to make your work easier.

Join the millions who've already saved time and money on many of their Office Equipment purchases by taking advantage of BuyerZone's FREE, no obligation services like:

- Quotes from multiple suppliers

- Pricing articles

- Buyer's guides

- Supplier ratings

- Supplier comparisons

#### **REQUEST FREE QUOTES NOW!** Call (866) 623-5564 or visit BuyerZoneBusiness.com

# One radio-test platform addresses development, production environments

ohde & Schwarz has 'announced a wideband-radio-test system that the company based on its 6-GHz CMW500 radio-test set. The new system will provide a single platform for both development and productiontest environments, and it spans all significant cellular and noncellular standards. The company aims to provide wirelessdevices makers, basebandand RF-chip-set providers, and network operators with a stable test system that will operate over many years.

As a wideband-radio tester, the single-chassis unit tests all layers from RF parametric measurements to protocols and applications. The CMW500 is a modular instrument, and the new platform will be modular in both hardware and software.

The unit combines RFgenerator and RF-analyzer functions. It supports GSM (global-system-for-mobile)communications Europe/ GPRS (general-packet-radioservice), WCDMA (wideband-code-division/multipleaccess)/HSPA (high-speedpacket-access), LTE (longterm-evolution), TD-SCDMA (time-division-synchronouscode-division-multiple-access), CDMA2000 1×RTT (onetimes-radio-transmissiontechnology), CDMA2000 1×EVDO (one-times-evolution-data-optimized), Mobile WiMax (worldwide-interoperability-for-microwave-access), WLAN (wireless-local-areanetwork), Bluetooth, DVB-T (digital-video-broadcastingterrestrial), and GPS (globalpositioning-system) standards. Multitechnology support handles test cases, such as handover and cell-selection procedures, in which multiple standards are in play.

In contrast to such layered development-test scenarios, in production test, you can configure the same basic platform to optimize it for minimum test time and, hence, cost. The company's Smart Alignment concept cuts alignment times by as much as 90%, and the unit's two complete channels allow parallel measurements to take place on two products-which need not employ the same standard. Using a single platform means that you can easily transfer to production test scripts you create in development.

Sending high data rates over nonideal radio channels involves complex protocollayer processes; the mobile must correct data packets with errors and handle multiple data streams in parallel. These fast processes, such as HARQ (hybrid automatic repeat request) and MIMO (multiple input/multiple output), run at layers 1 and 2 and require a tester that simultaneously performs protocol analysis and hardware-oriented RF measurements.

According to Anton Messmer, director of the company's mobile-radio-tester subdivision, in the early stages of working with a standard, you would have previously required a protocol tester and RF parametric measurements. Now, he says, one unit provides all the data and performs end-to-end testing of the complete communications link in realistic signal environments. Despite the economic downturn, cellular operators are still pressuring the company's leading customers to have LTE products ready for a 2010 rollout, Messmer adds. Increasingly, testing will encompass end-to-end systems measurements, such as real data rate and even battery life.-bv Graham Prophet Rohde & Schwarz, www2. rohde-schwarz.com.

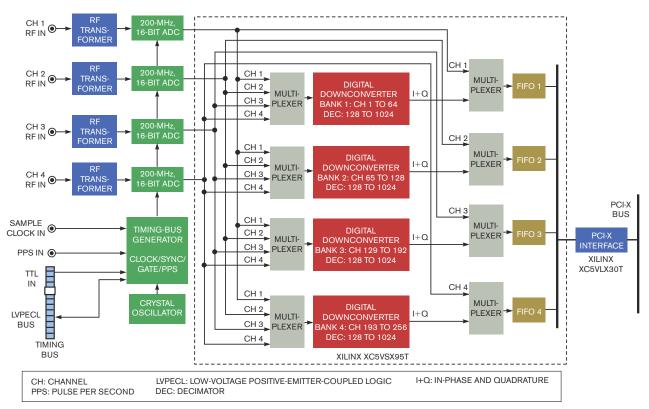

#### MEZZANINE MODULE USES FPGA TECHNOLOGY

**Curtiss-Wright Controls** Embedded Computing recently announced an I/O-mezzanine COTS (commercial-off-the-shelf) card that combines a userprogrammable FPGA and configurable I/O in a PMC (peripheral-componentinterconnect-mezzaninecard)/XMC (extendedmezzanine-card) form factor for applications such as imaging, system control for radar, softwaredefined radio, and signalintelligence platforms.

The XMC-FPGA05D combines reconfigurable-FPGA processing with high-speed datapaths.

The XMC-FPGA05D includes an onboard Virtex-5 FPGA to control the I/O interface and deliver as many as 138 signals, including signals for ADC, DAC, Camera Link, RS-485, and LVDS (low-voltage differential signaling), from its front panel and as many as 64 signals from the backplane through the host card. Prices for the XMC-FPGA05D start at \$7250.

For an expanded description of this product, go to www.edn.com/ 090319pb.

-by Warren Webb Curtiss-Wright Controls Embedded Computing, www.cwcembedded.com.

The CMW500 wideband-radio-test system handles wireless-test tasks.

# Everything sounds better, and plays longer, with Analog ICs inside.

#### Our newest portable audio innovations

#### MEMS Microphones

Superior Sound Quality: ADMP401 (analog) and ADMP421 (digital) Best-in-class noise performance with flat frequency response over the entire audible range. Support for the new PDM digital output format for microphones.

#### AUDIO COL

#### Low Power: ADAU1361 and ADAU1761

Low noise and low power for extended playback times. Support for analog or digital output microphones. Embedded SigmaDSP<sup>®</sup> digital audio processor for customizing the end user's audio experience.

#### Class-D Amplifiers

#### High Efficiency: SSM2315 and SSM2317

Low noise, filterless design with excellent pop-click suppression. First in industry with built-in automatic level control (ALC) for loudspeaker protection.

#### Processors

of portable applications.

Embedded Processing: Blackfin® Processor, ADSP-BF524C High performance, cost- and energy-efficient embedded processor enables true to life audio and video for a wide range

# High performance, low power. Hear why market leaders specify Analog Devices.

Portable device manufacturers rely on audio quality, and Analog Devices, to differentiate their designs. That difference starts by simplifying your development challenge: fewer components, the ability to more easily meet power and cost budgets, GUI programming, and readily available tools and technical support. Most importantly, the ADI difference includes a superb user experience—from unequaled audio fidelity, to custom effects with our library of algorithms, to smaller system sizes, to extended listening times.

Find out what manufacturers of leading media player, handset, PDA, and camera brands already know. Life sounds better with Analog ICs. Visit *www.analog.com/audio-ad1*.

analog is everywhere".

# pulse

# VOICES

### Chip design in recession: a view from an ASIC consolidator

There is no question that the recession, no matter what its future, is profoundly changing IC design. Investment patterns are changing, imposing huge and wrenching changes on engineers. And there are signs that the underlying models of the industry—integrated-device manufacturers, fabless-IC companies, and foundries—may change as well before we get through these trying times. Jack Harding, veteran of the design-automation and ASIC businesses and now at the helm of eSilicon, recently discussed changing times, changing models, and what they might all mean for designers. A portion of that discussion follows. For the full interview, go to www.edn.com/090319pc.

# What do you mean when you say that business models are in transition?

We're seeing executives revisiting all forms of fixed costs on their income statements. These are often companies that have already decided to go fabless, have outsourced back-end design, and [trimmed] their design teams. Now, they are starting to look at operations costs.

If a company is doing one chip design every 18 months, why would [it] keep an operations staff on the payroll? That [move] would be like keeping a full-time staff for mergers and acquisitions. So, we are seeing executives starting to ask, "Can someone take over production management for us?"

## And ASIC consolidators can offer that benefit?

We are basically an aggregator, but maybe we are best known as a fabless-ASIC company. Because we handle lots of designs per month, we very quickly get up the learning curve on back-end

design of new nodes. Instead of each new design's being a new experience, we are able to develop a fairly automated methodology at a new node. We are doing mostly 40- and 45-nm designs, for instance. At this stage, we are tuning the methodology to a manufacturing experience: working on yield and reliability optimization, where we can and cannot compromise with the foundry on design rules—things that come from experience.

But customers have taken us beyond just the design space. Because we are such a large customer to the foundries we work with, we have economies of scale and influence, and we are also skilled in managing product life cycles. As fabless companies understand this point, they see the possibility of changing the business model.

Basically, we can offer to take over responsibility for production on an existing product, deliver the chips to you at the price you have today, and meet the goals on your cost-reduction road map. And we can make money doing that.

In addition to looking at outsourcing operations, are you seeing the fabless-semi companies and system houses looking for other economies, such as postponing designs?

We are seeing every possible form of cash conservation. Companies are taking designs to RTL [register-transfer-level] freeze and then shelving them. They are delaying tape-outs. They are cutting wafer orders. The paradox of all this is that we as an industry are managing our resources better than we ever have before, but we are still seeing the worst situation.

The good news is that, because of all the attention the industry has paid to inventories since the Internet bubble, we may be in a better position than in the past. Companies we talk to expect to purge their inventories in one to three quarters, not two years.

And design doesn't come to a stop. Companies are still conducting R&D, and they are still doing algorithm development. One thing that might change, though, is the shocking amount of overdesign that has been common in the industry. Design teams may have used 65 nm for a design that would have worked just fine in 90 nm. They might have specified 600 MHz just for head room when the requirements were only 450 MHz. We may see a lot of that overdesign evaporating now as companies try to reduce their NRE [nonrecurring-expense] levels.

#### Reducing NRE-that must be music to the ears of FPGA companies.

You know, this is the A fourth major recession since the introduction of FPGAs, and their use model still hasn't changed. They are still a small fraction of the size of the ASIC/SOC [application-specific-integrated-circuit/system-on-chip] business. I think perhaps some people have misunderstood that [idea] because chip-design starts have been dropping, but that drop has been primarily because, with increased integration, one SOC will do what 10 ASICs used to do. The drop is not primarily because of FPGAs' displacement of ASICs.

Reality is that, today, if you can reduce the cost of a chip by 50 cents, that is justification enough to replace it in the bill of materials. In that kind of environment, you are not going to pay a huge premium for an FPGA.

#### Do you see the recession accelerating dispersal of design teams around the world?

No. Design teams will continue to outsource portions of the design, but we maintain that at a certain level of complexity, proximity of the lead engineers to each other and to the customer is absolutely vital. Dispersing tasks to outlying teams works only when there will be only low interactivity with the remote team and little or no customer involvement in that portion of the design.

-Interview conducted and edited by Ron Wilson

#### RAQ's

# **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

## Impedance Measuring Chip Offers Little Resistance to Applications

**Q:** I came across your Impedance measuring chip (IMC) in a recent article. It sounds interesting, but how does it work and what can it be used for?

**A:** The impedance measuring chip you mention is an extremely versatile device with countless practical applications.

Able to measure complex impedances from  $100\Omega$  to  $10M\Omega$  with 0.5% accuracy, the IMC is a marvelous example of integration, elegance and practicality. The IMC comprises a direct digital synthesis (DDS) frequency generator, a 12-bit analog-todigital converter (ADC), and a digital-signal-processing (DSP) engine.

The frequency generator provides a voltage stimulus to the device under test (DUT) at frequencies between 1 kHz and 100 kHz, and the ADC samples the resultant current. The DSP performs a discrete Fourier transform (DFT) on the digitized signal, and produces real (R) and imaginary (I) data words at each frequency. Using this information, the magnitude and phase can be calculated along any point in the frequency sweep.

Limited only by the imagination, some applications for an IMC include virus detection, blood coagulation monitoring, electro-impedance spectroscopy, and loudspeaker optimization.

Different virus strains cause different chemical reactions in blood. Characterizing these reactions by measuring their impedance over frequency enables researchers to identify different virus strains by their impedance signature.

Blood clotting time can be determined by measuring the impedance as it coagulates. Crucial to recovery of heart bypass patients, monitoring coagulation enables doctors to maintain a balance between bleeding and clotting.

Electro-impedance spectroscopy uses impedance to measure corrosion of aluminum and steel in infrastructure, cars, planes, and ships, preventing early failures and unneeded repairs. Impedance measurement chips can be placed in remote, hard to reach spots. This constant "structural supervision" signals maintenance crews to the first sign of corrosion or premature wear.

Measuring speaker impedance across the audio frequency range enables designers to actively match the speaker impedance to the audio driver for optimal performance and power transfer.

It's almost maple sugar season here in New England. I wonder if an IMC could measure the sugar content of the sap... hmm, I'll have to look into that.

To Learn More About Impedance Measurement Applications

http://designnews.hotims.com/23098-101

Contributing Writer John Ardizzoni is an Application Engineer at Analog Devices in the High Speed Linear group. John has been with Analog Devices since 2002, he received his BSEE from Merrimack College in N. Andover, MA and has over 29 years experience in the electronics industry.

Have a question involving a perplexing or unusual analog problem? Submit your question to: rag@reedbusiness.com

For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

## **Understanding FFT plots**

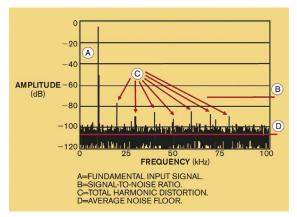

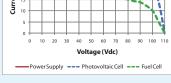

ou can generate an FFT (fast-Fourier-transform) plot by periodically collecting a large number of conversion samples from the output of an ADC. Typically, ADC manufacturers use a single-tone, full-scale analog input signal for the performance curves in product data sheets. You take data from these conversions and create a plot similar to the one in **Figure 1**. The frequency scale of this plot is always linear, from zero to the converter's sampling frequency divided by two.

You generate the plot by applying a sampling frequency of 100k samples/ sec to a 12-bit ADC with an analog input signal of 9.9 kHz. The signal at 9.9 kHz is the fundamental input signal (A). The fundamental input-signal spur reaches almost 0 dB.

The specifications of interest in an FFT plot are the fundamental input signal, the SNR (signal-to-noise ratio), the THD (total harmonic distortion), and the average noise floor. A useful way of determining noise in an ADC

circuit is with the SNR (B), the ratio of signal power to noise power. The SNR of the FFT calculation is a combination of several noise sources, including the quantization error of the ADC, the internal noise of the ADC, noise from the voltage reference, and noise from the driving amplifier. The theoretical limit of SNR is 6.02n+1.76 dB, where n is the number of converter bits.

The THD (C) quantifies the amount of distortion in the system. The THD is the ratio of the root-

mean-square sum of the powers of the harmonic components, or spurs, to the inputsignal power. Spurs resulting from the nonlinearity of the ADC appear as whole-number multiples of the input signal's frequency, or fundamental frequency. Most manufacturers use the first seven to nine harcomponents monic in their THD calculations.

If the ADC creates spurs, it most likely

has some INL (integral nonlinearity) errors. Spurs can also come from the input signal through the signal source or the driving amplifier. If the driving amplifier is the culprit, it may have crossover distortion, be unable to drive the ADC, or be bandwidth-limited. Injected noise from other places in the circuit, such as digital clock sources or the mains frequency, can also create spurs in the FFT result.

In an FFT representation of converter data, the average noise floor (D) is a root-mean-square combination of all the bins within the FFT plot but excludes the input signal and signal harmonics. You should choose the number of samples versus the number of ADC bits so that the noise floor is below any spurs of interest. With these considerations in mind, the theoretical average FFT noise floor is  $6.02n+1.76 \, dB+10 \log[(3 \times M)/$  $(\pi \times \text{ENBW})$ ], where M is the number of data points in the FFT, ENBW is the equivalent noise bandwidth of the window function, and n is the number of bits of the ADC. A reasonable number of samples for the FFT of a 12-bit converter is 4096.EDN

#### REFERENCES

"FFT Applications for TDS Oscilloscopes," Tektronix, April 6, 2005, www.tek.com/Measurement/App\_ Notes/fft/eng/55W-8815-2.pdf.

"C24x Fast Fourier Transform (FFT) Library," Texas Instruments, focus.ti.com/docs/toolsw/folders/ print/sprc069.html.

Bonnie Baker is a senior applications engineer at Texas Instruments and author of A Baker's Dozen: Real Analog Solutions for Digital Designers. You can reach her at bonnie@ti.com.

+ Go to www.edn.com/090319bb and click on Feedback Loop to post a comment on this column.

+ www.edn.com/bakersbest

**NORTH AMERICA** +1 800-625-4084

**ASIA PACIFIC** +852 2376-0801

**JAPAN** +81 (3) 5226-7757

**EUROPE/UK** +44 (0) 1628-891-300

# Say Hello to a New Leader in Portable Audio ICs

When it comes to chips for portable audio applications, Cirrus Logic has quickly become an innovation leader. Cirrus Logic's portable audio IC products focus on minimizing current consumption, maximizing integration and reducing—or altogether removing—other components from board designs. Our customers value the innovation we provide, and so can you!

#### CS42L55 24-BIT CODEC FEATURES

- Ultra-low power audio codec uses only 5 mW in quiescent playback mode

- Patent pending bi-modal Class-H headphone driver

- Pseudo-differential ground centered outputs eliminates large, costly DC blocking capacitors

- Tiny 5x5 mm 36-pin QFN package (0.45 mm height)

- Operates from a single power supply of 1.8 or 2.5 V

# LEARN MORE AT

#### Cirrus Logic. We make it easier for you.

© 2008 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners.

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

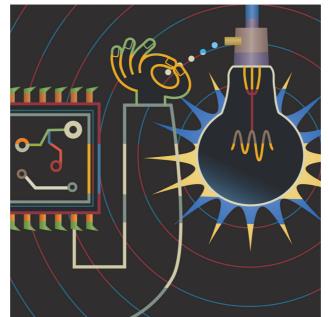

## One sensor does the work of many

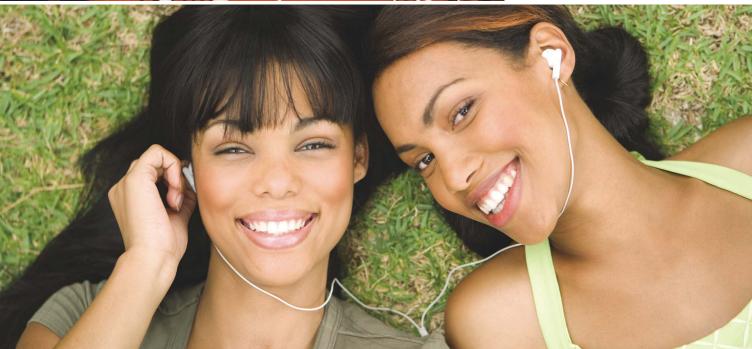

igital cameras, still relatively inexpensive devices, have exponentially increased the number of pixels they can capture. Because silicon, a primary material in CCD (charge-coupled devices) and CMOS imagers, is sensitive to the same wavelengths as the human eye, digital cameras have been able to double their pixel resolution roughly in step with the doubling in memory sizes.

Rice University is now demonstrating a camera that uses a single sensor to capture images that conventionally require an array of sensors (image courtesy Richard Baraniuk, Rice University). The researchers direct a captured image at a single sensor and use the resulting stream of measurements to reconstruct the image. They accomplish this task without making individual measurements of each pixel.

The second lens captures the reflected light from the DMD array and focuses all of the light to a single pixel-sensor collector. Because all of the reflected light goes toward the sensor, it effectively receives a summation of all of the reflected light. This approach differs from a conventional sensor array in which each pixel sensor receives only a fraction of the total light because each one receives only the light corresponding to a specific pixel location.

The analog-to-digital-conversion step is simpler because the system converts data from only the single pixel sensor rather than sequencing through the entire range of pixel locations in the image.

SCENE

TI based the DMD on its DLP (digital-lightprocessing) technology, which digital televisions and projectors typically use. Using a pseudorandom-number generator, the system configures a random set of half the DMDs in the array so that they reflect the incoming light to a second lens. The remaining DMDs reflect none of the light directed toward them. Each image snapshot uses a different random mix of reflecting and nonreflecting positioning of the DMD.

By tracking the random, half-reflecting-DMD-array configuration with the detected summation of light at the single-pixel sensor, the system applies a compressive-sensing-recovery algorithm across a series of snapshots to reconstruct the image. With this approach, the number of measurements of the scene necessary for adequate reconstruction of the image is only, say, 10, 20, or 40% of the total number of pixels in the image. A seed value for the pseudorandom-number generator manages the random configuration of the DMDs. The system uses this seed value to reconstruct and associate each configuration of the DMD array with the reflected-light-summation value.

The system sends the

image.

#### THAT'S MODEL-BASED DESIGN.

To create a two-mode hybrid powertrain, engineers at GM used models to continuously verify their design, test prototypes, and automatically generate the embedded code. The result: a breakthrough HEV, delivered on time. To learn more, visit mathworks.com/mbd

# All the power and flexibility of V·I Chip<sup>™</sup> technology in a brick format

A new, advanced modular power platform called VI BRICK<sup>TM</sup> — incorporating the superior technical attributes of V•I Chip technology and robust packaging — is now available.

VI BRICKs provide increased power capabilities and greater design flexibility. They

- Simplify thermal management

- Come in a compact and low profile package

- Are RoHS compliant and compatible with lead-free wave soldering processes.

#### The VI BRICK family consists of:

- Highly efficient bus converters (14 models)

- Separate modules for both regulation (PRM) and transformation / isolation (VTM) (18 models)

- High efficiency, power dense DC-DC Converters from 1.0 to 48 V (13 models)

Learn what this new powerful, flexible and growing family of power products can do for you. For more information call 800-735-6200 or go to *vicorpower.com/vibrick*.

Power at your command

Λlin

VICOR

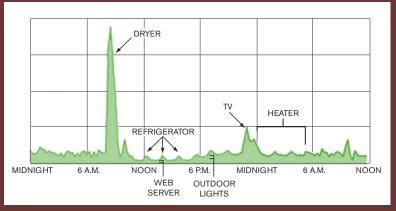

UTILITIES ARE PUSHING TO REPLACE OLD ELECTROMECHANICAL METERS WITH MICROCONTROLLER-BASED SMART METERS THAT, IN ADDITION TO THEIR INTELLIGENCE AND COMMUNICATION ABILITY, ARE ALSO TAMPER-PROOF. THERE IS ALSO A GROWING MARKET FOR INDIVIDUAL SMALL POWER METERS AND AN EMERGING MARKET FOR METERING AT THE SERVER, OR INDIVIDUAL-APPLIANCE-NETWORK, LEVEL.

# TAMPER-RESISTANT SMART POWER DEERS RELATION ISOLATED SENSORS

200

ost residences and commercial buildings in the United States currently use an old-style electromechanical utility power meter to track electricity use. The meters are reliable and cheap but hopelessly inadequate for use by a power-distribution system that requires accurate, repeatable power metrics as well as wired or wireless communications—in other words, the coming Smart istribution system

#### Grid electrical-power-distribution system.

The Smart Grid depends on smart meters with sophisticated communication capabilities to monitor energy usage and allow residential and business consumers alike to make informed choices about how much energy to use and when to consume it. The Smart Grid faces difficulties, though. Although, at the federal level, Washington has passed legislature such as the 2007 energy bill and the 2009 stimulus plan, utilities actually deploy power on a state-by-state basis. California and Texas are the states most aggressively moving toward smart metering in preparation for the Smart Grid (**Reference 1**).

Regardless of whether the Smart Grid in some form will proceed at the national level smoothly and seamlessly, enough individual utilities are purchasing and installing electronic power meters to make this market significant. Look at the important applications of the past 20 years: cell phones, computers, large-screen TVs. They make their mark because they have a market in the hundreds of millions. Utility-installed power meters have a similarly powerful market. Every house and commercial building requires one. Utility companies could replace 500 million meters worldwide over the next 10 years.

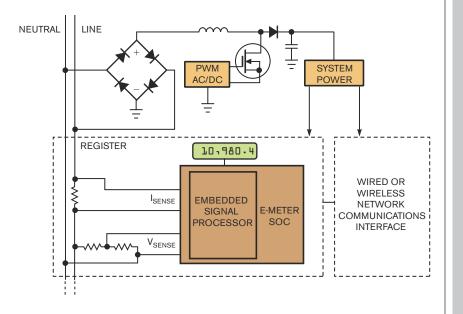

Smart power meters comprise a mi-

crocontroller with onboard ADC and DAC, a sense component for both voltage and current, an ac/dc-power converter, battery backup, and wire-less or wired communication capability (Figure 1).

Power-meter ICs are available from companies including Texas Instruments, On Semiconductor, Maxim, Analog Devices, Teridian, and Ev2. These ICs are essentially microcontrollers that track power-usage information as well as information back from the utility. They can perform some DSP calculations on voltage waveform and quality, communicate the information to a display, and store the information to be sent. Although the term smart meter indicates that the microprocessor is the central component, antitampering precautions make selection of the current-sensing component and even power backup important decisions for smart meters.

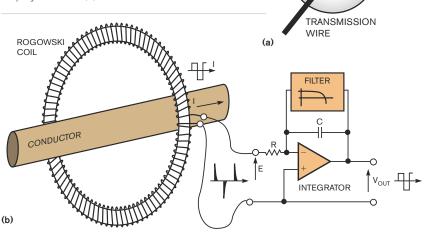

There are three main types of currentsensor technology for power meters: current transformers, Rogowski coils, and resistive shunts. The technology you use depends on whether the power distribu-

#### AT A GLANCE

Implementing the Smart Grid requires utility meters with electronic intelligence, tamper-proof electronics, and backup power.

Magnetic and inductive fields do not affect shunt-based current sensors, as they do current transformers and Rogowski coils.

Current transformers and Rogowski coils are inherently isolated sensors.

Backup power sources allow power meters to record and transmit power-outage data when ac power is unavailable.

tion is multiphase or single-phase. Most homes worldwide use only one phase from the generator coming to the wiring of the house. The US residential market uses a split-phase distribution that delivers 120V ac and as much as 240V ac to residences and requires a current transformer as the isolated voltage/current sensor. Commercial and some residential deployments in northern Europe

MASS S05-L

use three-phase, but homes are usually single-phase. In general, when sensing voltage and current to determine power usage in metering, you use a shunt resistor on single-phase distribution systems and a current transformer or Rogowski coil in a split- or three-phase system, because measuring the voltage across different phases can exceed the voltage tolerance of semiconductor devices.

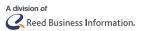

The most popular isolated sensors are current transformers, Rogowski coils, and Hall-effect sensors, roughly in order of popularity (Figure 2). A current transformer has an iron core and is susceptible to tampering with a large permanent magnet. A magnet next to the transformer can saturate the core so that the sensing coil can't pick up the ac field in the power line. A Rogowski coil has an air core and consists of a coiled piece of wire that wraps around the power line. Unlike an iron core, the air core doesn't saturate in the presence of a large permanent magnet. However, it's susceptible to other tampering methods, such as the presence of a large inductive field that couples into the coil and over-

# absolutely economic

#### MTM Power, Inc. AC/DC Modules

The climate change takes its toll. If you do not want to disregard progressive technique, real innovations for energy saving are mandatory.

The AC/DC power modules of MTM with 5 – 100 W significantly reduce the power consumption during standby.

Due to the worldwide unique thermoselective vacuum encapsulation, the AC/DC modules of MTM Power are resistant against shock and vibration as well as dust and humidity.

## Hotline: +1 781 828 2022

info-inc@mtm-power.com www.mtm-power.com

Figure 1 Smart power meters comprise a microcontroller with onboard ADC and DAC, a sensing component for both voltage and current, an ac/dc-power converter, battery backup, and wireless or wired communication capability.

whelms the ac current the coil is meant to sense.

Hall-effect sensors rely on a semiconductor device to sense the magnetic field caused by the alternating line current. But their readings can vary with temperature and are not always linear over a wide range of current. This problem is more significant in the US market, in which meters are rated as high as 200A, than in, say, India, where meters measure 20 or 40A. "Linearity becomes important in a market like the United States," says Kourosh Boutorabi, Teridian's vice president and general manager of the meter-products-business unit. "The requirement by utilities is for meters to have 0.2% error. Tolerances in the rest of the world are closer to 1% error. If you're consuming more power, then more loss in measuring is more important, and accuracy in measuring is more important."

Hall-effect sensors have advantages, too, he says. "Although they are not as accurate as [current transformers], they are cheaper." A Hall sensor can be pushed against [the power line] with no physical interconnection." With a current transformer, you have to manually assemble the power line and the sensing coil.

Most power meters worldwide are sin-

gle-phase and use a simple shunt resistor as a current-sensing element. Cathal Sheehan, product-marketing manager for Bourns' resistive-products division, characterizes shunts as simple, inexpensive, and unaffected by the magnetic and inductive fields that befuddle magnetic and inductive sensors.

Mark Strzegowski, energy-meteringproducts-marketing engineer at Analog Devices, agrees that shunts provide no isolation between multiple phases, so you need to provide the isolation elsewhere. The company's approach is to use a shunt resistor with an isolating planar transformer it bases on the company's iCoupler technology for the isolating component: The iCoupler and shunt resistor combined are still cheaper than the cost of a current transformer or Rogowski coil, and they still preserve measurement linearity. "One of the things important to consider in selecting a current-sensing technology is the performance that the customer is looking for," says Strzegowski. "There has been a trend in the market toward wider dynamic ranges and also adding more measurements. You need to accurately measure 100A current all the way down to 100-mA current, with the same level of accuracy, since 0.1% is a typical accuracy spec."

## Amped Up! Ready to Go!

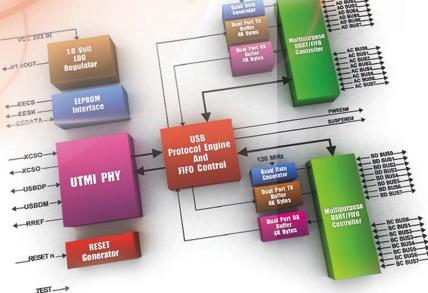

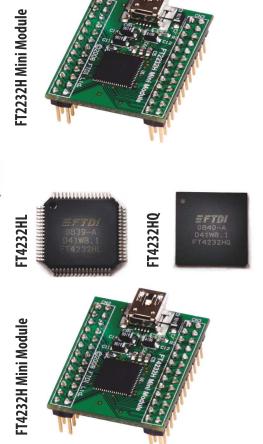

# USB in the FAST LANE

## FT2232H / FT4232H High Speed USB Interface ICs

#### FEATURES

FT2232H (Dual High Speed USB to Multipurpose UART/ FIFO IC) has 4k bytes Tx and Rx data buffers per interface.

FT4232H (Quad High Speed USB to Multipurpose UART/MPSSE IC) has 2k bytes Tx and Rx buffers.

Multi-Protocol Synchronous Serial Engines (MPSSE), capable of speeds up to 30Mbits/s, provide flexible interface configurations.

Entire USB protocol on a chip with integrated LDO regulator and PLL. Extended temperature range (-40°C to +85°C).

T2232H0

# Visit us at the ESC Silicon Valley in the Main Hall, Stand 1729

Learn today. Design tomorrow.

Future Technology Devices International Ltd. (FTDI) www.ftdichip.com

FT2232HL

Figure 2 A current transformer's iron core is susceptible to tampering with a large permanent magnet. When you place it next to the transformer, the magnet can saturate the core so that the sensing coil can't pick up the ac field in the power line (a). Rogowski coils have an advantage over current transformers because they employ air cores (b).

Shunts have inherent problems with heating: Although their response is fairly linear, they can't handle some of the largest loads because of their self-heating effect. Likewise, current transformers typically have a small phase distortion that requires compensation, especially when applications require more sophisticated measurements, such as reactive- and harmonic-energy measurements. In general, single-phase powerdistribution meters have shunt resistors for sensors, and three-phase meters have current transformers.

Silvestro Fimiani, product-marketing manager at Power Integrations, argues that, in addition to its being tamperproof, efficiency in a power meter is important, especially because there is the potential in the near future to install or replace more than 100 million power meters worldwide. "Over the life of the meter, you can waste as much as \$20 in energy costs due to inefficient power usage in a meter," he says. "This [amount] can be as great as the cost of the meter." Fimiani may be a relatively lonely voice in the wilderness of smart meters calling out for power efficiency: Few other vendors are concerned with meter efficiency, possibly because the purchaser of meters, usually a utility, is not the entity that pays for the meter's power consumption. That cost is invisible but passes on to the consumer.

The components in a power meter should consume little power not only for the sake of cost savings and efficiency, but also to make sure that the meter operates efficiently when battery-powered. It's strange to think of a power meter's relying on battery power, but smart meters must be able to continue to operate even when there is a power outage.

The importance of battery backup in power meters depends on the region. In the United States, for example, if the power is down, there's nothing to measure, so there's little need to have the meter awake. Strzegowski of Analog Devices points out that, in India, however, some specifications require that there must be two batteries in the system. One powers meter reading and information storage for 24 or 48 hours and keeps the display alive. The other retains the meter information for as long as two years to prevent meter tampering. It removes the meter from the power line so that there is no voltage available to the meter electronics, but power is still flowing in the line.

Battery backup for power meters is often in the form of a lithium-thionyl battery, which has a self-discharge rate in the nanoamp region and a shelf life that exceeds 10 years. Tadiran is the largest manufacturer of these batteries in the United States. The battery alone is enough to back up data in the meter but

# Direct Online Ordering

# Check real-time availability

Order with your credit card

(F) Ships within 2 business days

intersil.com/ibuy

## the EVOLUTION of ANALOG™

## Precisely What You Need!

#### Micropower Precision Op Amps

# Main Instrumentation Amplifiers

# Current-Sensing Amplifiers

#### Precision Voltage References

Analog-to-Digital Converters

#### Digital Potentiometers (DCPs)

intersil.com/pinpoint

## the EVOLUTION of ANALOG™

not to burst data out in a wireless communication. One approach is to use the battery to trickle-charge a supercapacitor. Pierre Mars, vice president of applications engineering at supercapacitor manufacturer Cap-xx, explains how government regulations affect the meters: "Even though the meter is connected to the mains and there is abundant power, the meter cannot use it to transmit data,' he says. "One example is where I live in Australia, where the rules are [that] the meter cannot draw more than 2W of the user's power, so they need to use a [supercapacitor] to provide the burst power for GSM [global-system-for-mobile] communications transmission, which requires up to 6W for 0.6-msec bursts, with average power less than 0.75W." Mars notes that, if the government had written the rules in terms of energy used, rather than limiting peak power drawn, there would have been no problem.